Potrzebny sprzęt

- Rysino

- kabel USBmini

- programator USB Blaster JTAG

Oprogramowanie

Quartus II jest środowiskiem programistycznym dostarczonym przez firmę Intel dla produkowanych przez nią układów FPGA. Aby go pobrać musimy założyć darmowe konto. Możemy to zrobić na stronie firmy Intel. Później pobieramy oprogramowanie ze pod adresu fpgasoftware.intel.com.Będą nam potrzebne:

- Quartus Prime (includes Nios II EDS)

- MAX 10 FPGA device support

Warto od razu zainstalować także symulator:

- ModelSim-Intel FPGA Edition (includes Starter Edition)

Dla konwertera FT230 USB/UART może być potrzebny dodatkowy sterownik. Można go pobrać z pod adresu www.ftdichip.com/Drivers/VCP.htm.

Programujemy FPGA

Teraz możemy podłączyć programator USB Blaster do złącza JTAG na płytce Rysino. "Wypustka" złącza musi znaleźć się na górze, tak jak pokazuje to Rys. 1. Następnie podłączamy Rysyino i USB Blaster do portów USB komputera.

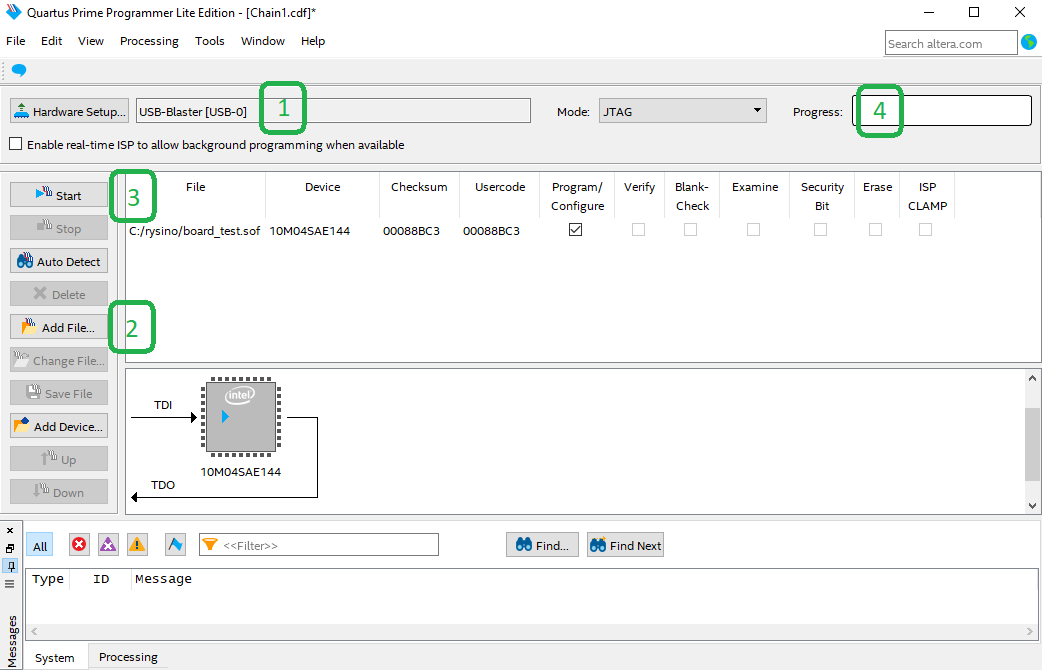

Następnym krokiem jest wgranie testowego bitstreamu: board_test.sof. Uruchamiamy Programmer (Quartus Prime 18.1). Jego okno pokazuje Rys. 2.

W polu (1) widzimy informację o wykryciu programatora USB Blaster.

Klikamy przycisk Add file (2) i wybieramy plik board_test.sof.

Naciskamy Start (3).

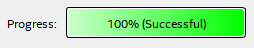

Postęp jest prezentowany w polu (4). Po kilku sekundach zobaczymy "100% (Successful)" (Rys. 3).

Tą samą procedurę przedstawiono także w filmie:

Bitstream testowy

Po zaprogramowaniu można zacząć zabawę z płytką:

- LED1-4 pokazują liczby od 0 do 15 (w systemie binarnym).

- LED5-8 są sterowane za pomocą przełączników.

- UART pracuje w trybie "echo".