Co w FPGA siedzi

Środowisko Quartus pozwala na sprawdzenie w jaki sposób nasz projekt został zrealizowany w układzie FPGA. W tym krótkim wpisie pokażę jak to można sprawdzić.

Materiał jest dostępny w wersji video oraz tekstowej.

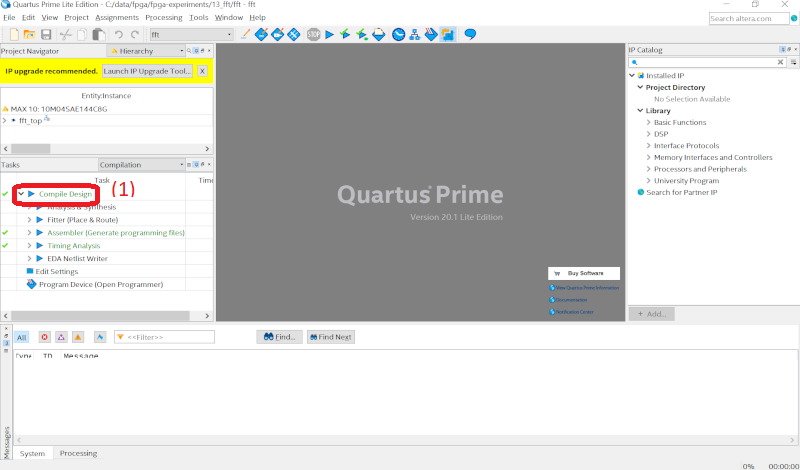

Jako przykład posłuży nam projekt FFT, który można pobrać z repozytorium. Po uruchomieniu zobaczymy główne okno programu Quartus (rys 1). Uruchamiamy budowę projektu klikając Compile Design (1).

Rysunek 1. Główny ekran programu Quartus

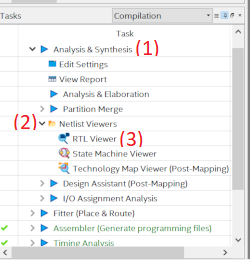

Następnie z znajdującego się po prawej stronie okna Task, rozwijamy: Analysis&Synthesis (1) -> Netlist Viewer (2) i wybieramy RTL Viewer (3), tak jak pokazano na Rysunku 2.

Rysunek 2. Menu Task

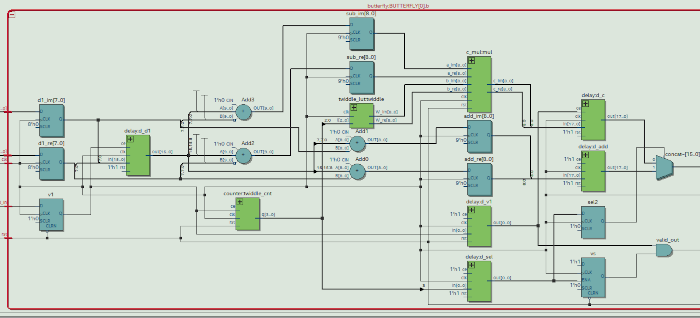

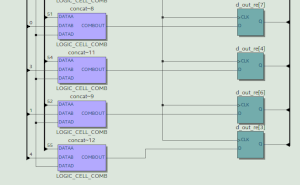

Otworzy się nowe okno, w którym zobaczymy nasz projekt rozrysowany na poziomie RTL (Register-transfer level). Jest to wysokopoziomowy sposób pokazywania logiki. Nie jest on związany ze strukturą układu FPGA (Rysunek 3).

Rysunek 3. Fragment widoku RTL

Następnie przejdziemy do kolejnego widoku: Technology Map Viewer (Post Fitting). Prezentuje go Rysunek 4.

Rysunek 4. Technology Map Viewer (Post Fitting)

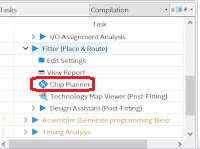

Tutaj już widzimy tylko elementy, które są dostępne w układzie FPGA. Mamy jeszcze drugi, pokrewny widok Technology Map Viewer (Post-Mapping). Jest on podobny, ale tym razem poszczególne bloki są przyporządkowane do konkretnych miejsc w strukturze układu. My jednak przejdziemy do kolejnego widoku. W zakładce Task rozwijamy Fitter i wybieramy Chip Planner (Rysunek 5).

Rysunek 5. Menu Task

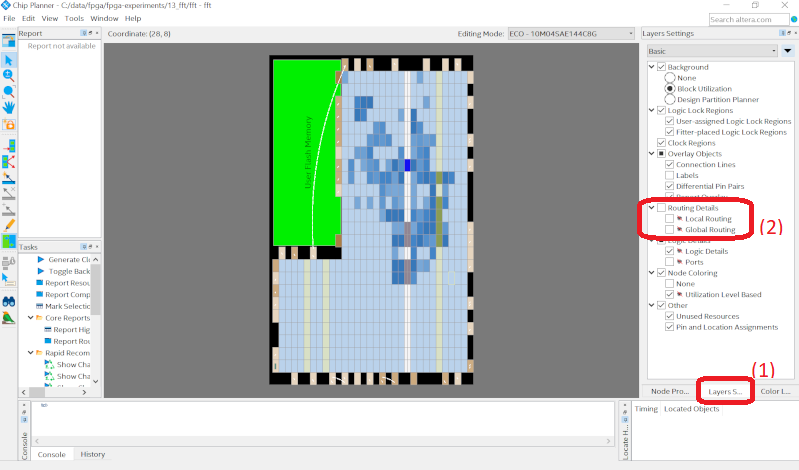

Gdy go wybierzemy zobaczymy okno podobne do tego z Rysunku 6.

Rysunek 6. Chip Planner

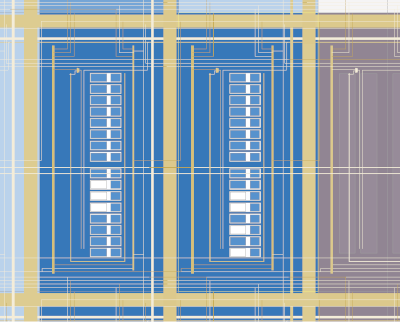

Widzimy tutaj strukturę układu FPGA. Kolorem niebieskim zaznaczone są bloki CLB, zielonym RAM, a brązowym DSP. Gdy przybliżymy, zobaczymy wewnętrzną budowę poszczególnych bloków, oraz które ich części są użyte. Możemy także włączyć widok połączeń. W lewym menu wybieramy zakładkę Layers (1) i zaznaczamy Routing Details (2). Uzyskany wynik prezentuje Rysunek 7.

Rysunek 6. Widok połączeń pomiędzy blokami

Mam nadzieję, że ten krótki opis zachęci Was do samodzielnego sprawdzania jak Wasze projekty są implementowane. Pozwala nam to lepiej zrozumieć układ i wykorzystać jego możliwości.